- O flash de 5 bits de célula dividida SK Hynix aumenta a densidade do SSD sem reduzir significativamente a complexidade da produção

- A paralelização estilo RAID-0 de NAND particionada aumenta significativamente a velocidade de leitura

- Cada meia célula reduz a queda de tensão, ampliando a resistência do flash de cinco bits

A indústria flash NAND continua procurando maneiras de aumentar a densidade de armazenamento à medida que aumenta a demanda de data centers, dispositivos de consumo e ferramentas de IA.

O dimensionamento convencional por meio de camadas NAND 3D adicionais tornou-se cada vez mais complexo, caro e difícil de fabricar de forma consistente.

Embora o flash QLC de quatro bits já esteja em produção comercial, a transição para o flash PLC de cinco bits tem sido impossível devido a problemas de confiabilidade e resistência relacionados às limitações do sensor de tensão.

Como o flash de célula dividida muda a equação

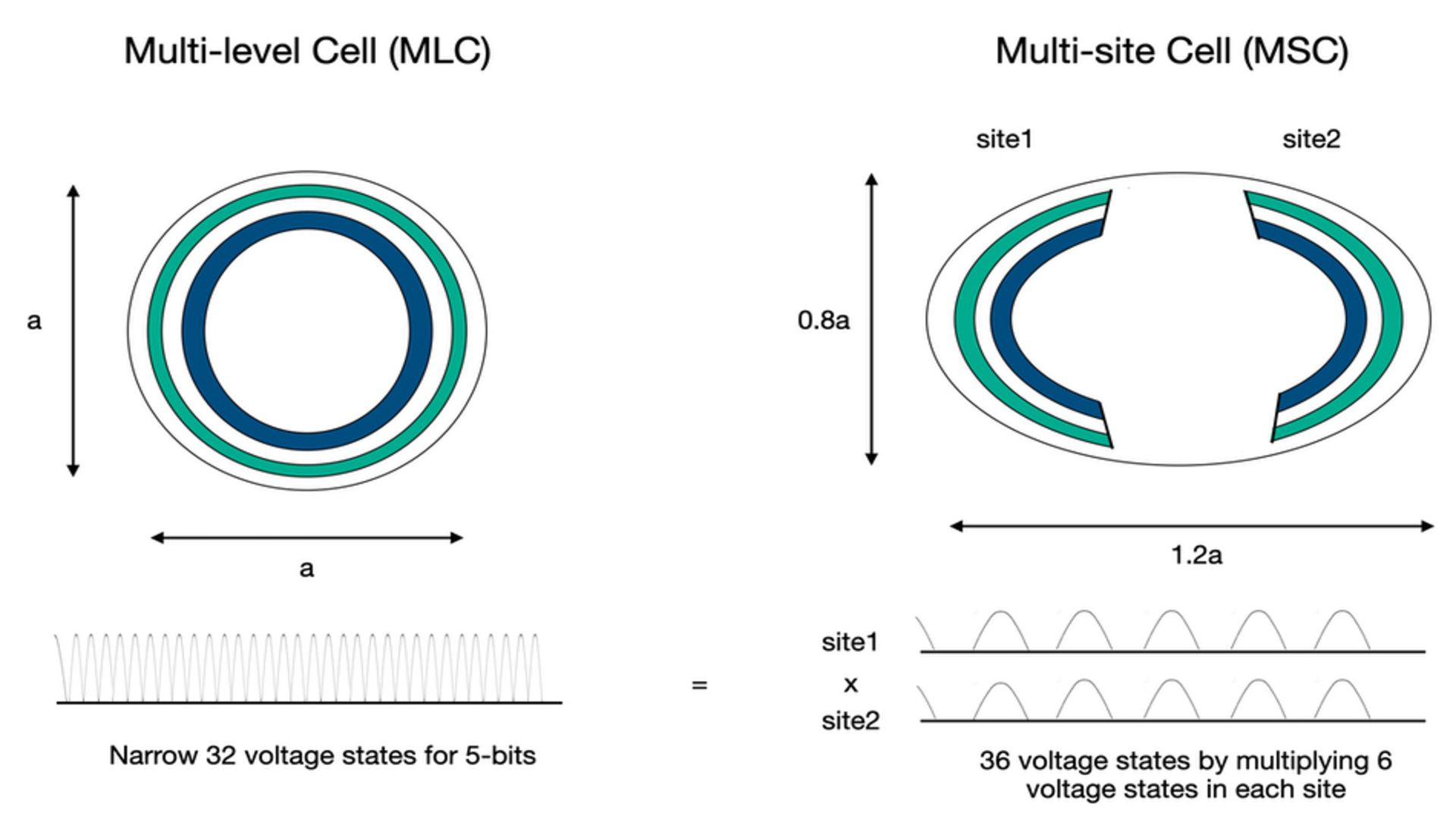

A SK Hynix introduziu outra abordagem conhecida como tecnologia de células multi-site. Em vez de forçar uma única célula NAND a ter 32 estados de tensão, o projeto a divide em duas meias-células independentes.

Cada metade armazena seis estados de tensão, que se combinam para representar um valor de cinco bits. Este design reduz o acúmulo de tensão enquanto mantém a densidade geral de bits.

As duas meias células operam em paralelo como uma única unidade lógica, semelhante à forma como o RAID-0 espalha os dados pelos discos rígidos para aumentar o desempenho.

Neste caso, os estados de tensão são combinados através do acesso em vez de serem desenhados em dispositivos separados.

A forma física da célula é elíptica em vez de circular, o que deixa espaço para uma parede isolante entre as metades e conexões de linhas de bits separadas.

SK Hynix afirma que a maior lacuna de tensão em cada meia célula reduz o vazamento de elétrons e encurta o tempo de programação.

Ambas as metades são lidas simultaneamente, o que, segundo a empresa, oferece velocidades de leitura mais rápidas em comparação com projetos de PLC convencionais.

Este método também melhora a resistência, pois a tensão mais baixa reduz o desgaste da célula.

A SK Hynix demonstrou wafers funcionais na conferência IEDM de 2025, indicando que o conceito vai além da simulação.

A abordagem de célula dividida requer etapas adicionais no processo de semicondutores, incluindo divisão celular e preenchimento de lacunas, o que aumenta custo e complexidade.

Enquanto a SK Hynix avalia a capacidade de fabricação, espera-se que outros fabricantes de flash, incluindo Samsung, Micron, Kioxia e Sandisk, explorem ideias semelhantes.

O conceito não promete SSDs mais baratos, mas sim mais compactos, e não elimina o papel dos discos rígidos no armazenamento em grande escala.

Se os fabricantes puderem produzir células multi-site em escala, o flash PLC poderá finalmente ser viável sem as sérias desvantagens vistas em projetos anteriores.

Através Blocos e arquivos

Siga o TechRadar no Google Notícias e adicione-nos como sua fonte padrão para receber notícias, opiniões e opiniões de nossos especialistas em feeds. Certifique-se de clicar no botão Continuar!

E é claro que você também pode Siga o TechRadar no TikTok para receber novidades, análises, unboxings em formato de vídeo e receber atualizações constantes nossas WhatsApp também